Thrust 1: Chip Design Cycle Reduction

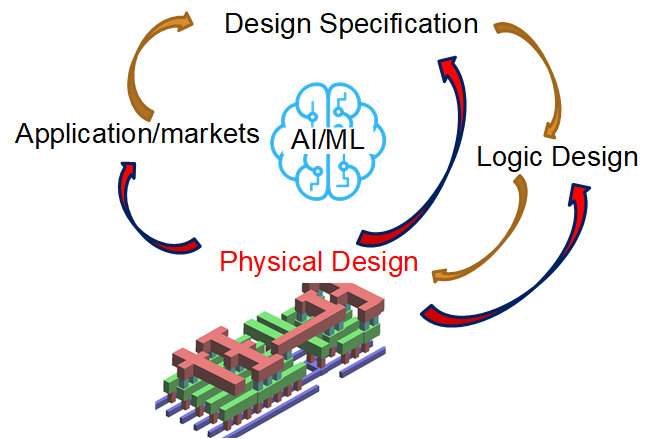

The goal of this research is to reduce the design time across all stages of chip development, from design space exploration, logic design and frontend implementation up to the physical design and signoff stages.

AI/ML-Assisted Design Space Exploration

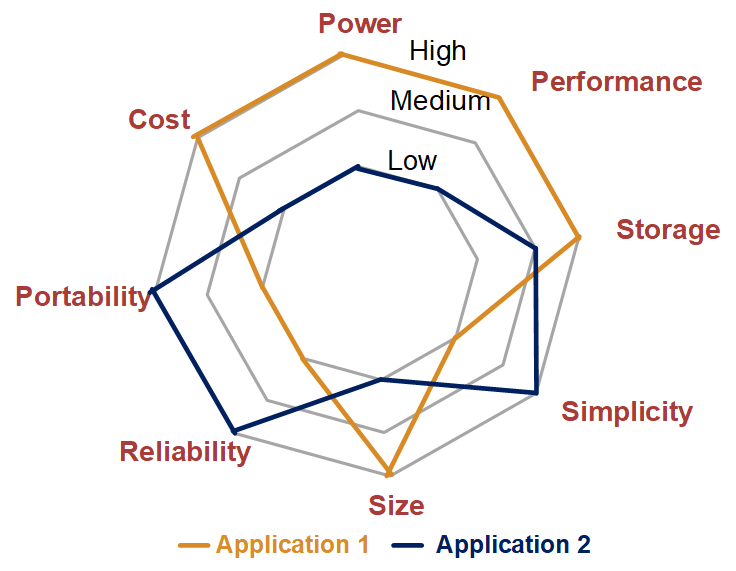

As the application space stays as diverse as ever, designing chips for different applications will require very different approaches. For example, designing an IoT chip is very different from designing a processor chip. It was because that these systems need to be optimized for the design targets and constraints dictated by the specific needs of the application. Thus application space started to shift significantly from one type of application to another. In this project, we explore how AI and machine learning techniques can be leveraged to find the sweet spot among a large design space. Ongoing projects include:

- Pre-RTL design space exploration tools

- Efficient design partition techniques

- Process corner reduction techniques in advanced technology nodes

AI/ML-Assisted Design Automation (EDA) Techniques

With the increasing needs of fitting more functionality on a single chip and growing complexity of design rules/signoff conditions at newer process nodes, chip design criteria becomes more stringent and designers have to go through more iterations to achieve multiple design goals. Huge run time penalty and massive human errors are involved in closing the design in the backend. Although major EDA companies have taken some early steps to incorporate certain levels of intelligence in their tools, it is still in a very conservative testing mode, which is far from the production quality. In this research direction, we explore intersections of AI/ML algorithms with traditional EDA problems such as synthesis, placement and signoff.

Agile Hardware Development

The concept of agile design originates from the software community, where it brought a renewed emphasis on teamwork and deliverable as opposed to the compartmentalizing disciplines. To enhance the productivity of the agile approach, we explore productivities of high level design approaches such as HLS or construction languages. Another aspect we actively look into is open-source EDA. The advent of open-source concept in the hardware community shines some lights on agile design through massive collaborative efforts. We would like to explore the opportunities offered by open-source tools and flows, research the interface between open-source hardware and non open-source hardware, overcome the barriers when adding more common building blocks.

Thrust 2: Design for Low Power & High Reliability

In this research, we start from a spectrum of applications where various types of chips are adopted. We look at two very important design metrics that concern the designer of the chips. They are power and reliability. Power is critical for almost every chip, and reliability is gaining growing interests for many applications. We try to find design solutions that are across the system hierarchy, also we explore the correlation between the two, and develop codesign methods that optimize both.

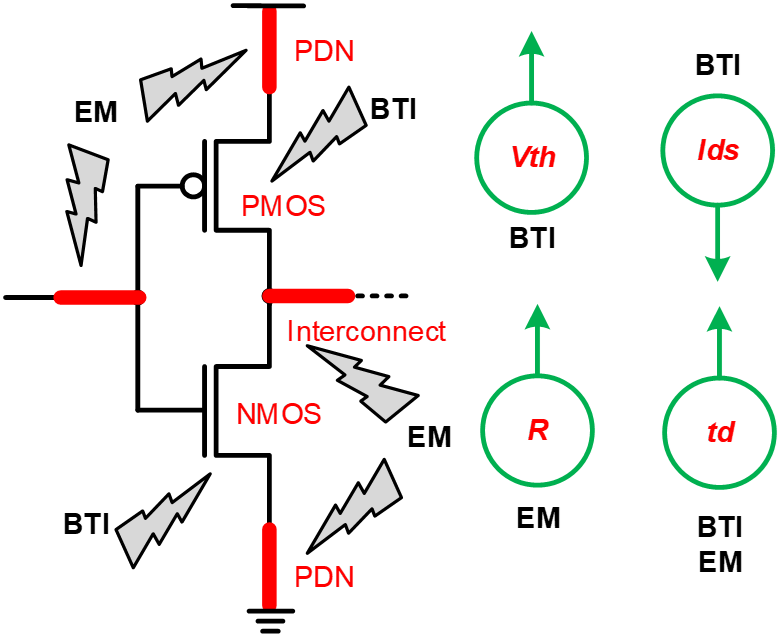

Aging-aware Design Techniques

Nowadays, on a computer chip with size of a fingernail, there are billions of transistors that serve as the smallest computing units. Just as in the biological world, these transistors and their interconnects will age with time, the degradation over time leads slowly but surely to decreased switching speeds, and it can even result in outright circuit failures. It is also unfortunate that aging is becoming much more troublesome for design teams at10nm and below. From application perspective, reliability has become an increasingly concern for self-driving cars, trust AIs and smart health systems. The reduction in PPA, coupled with a demand for longer lifetime from the application spaces, has pushed the designers to examine alternative approaches to deal with aging issues instead of assigning conservative static margins as what has been done for a long time. In this project, we explore different approaches to combat reliability threats to extend the lifetime and improve the performance. Eventually, we deliver a reliable chip that can be adapted into various scenarios.

Ultra-low-power and Energy-efficient Architectures

AI and machine learning accelerator design is beginning to shift directions as more computing moves to the edge, adding a level of sophistication and functionality that typically was relegated to the cloud, but in a power envelope compatible with a battery. This research explore design and architecture solutions to further lower the power and optimize for energy efficiency. We look at high performance AI chips, low power battery-operated chips to ultra-low power bio-medical chips. Different low power techniques are required at circuit level, architecture level and system level. We aim to find the most efficient low power solutions for different application scenarios. We also explore the factors that set the power limits, such as novel cooling techniques and emerging devices.